Alex Frid

Classifying the Valence of Autobiographical Memories from fMRI Data

Sep 10, 2019

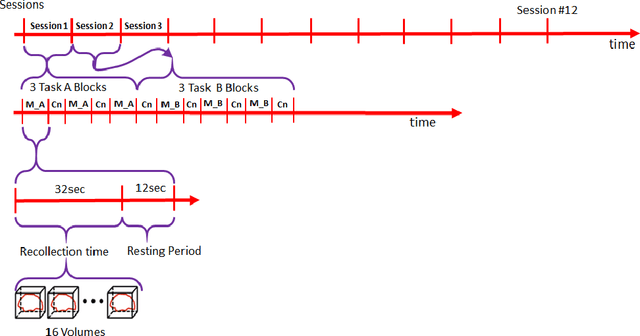

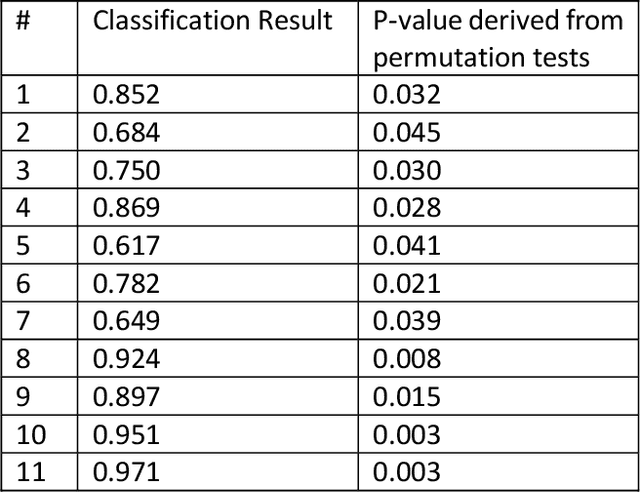

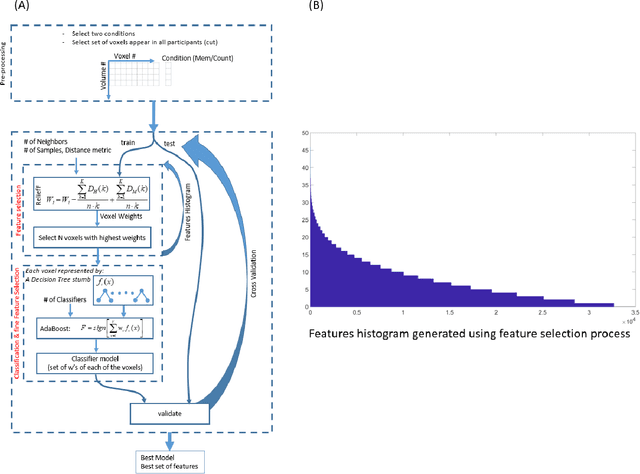

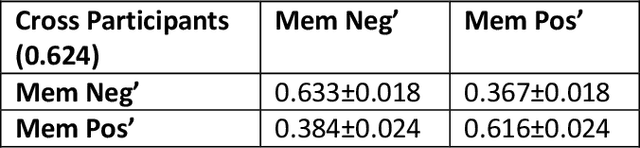

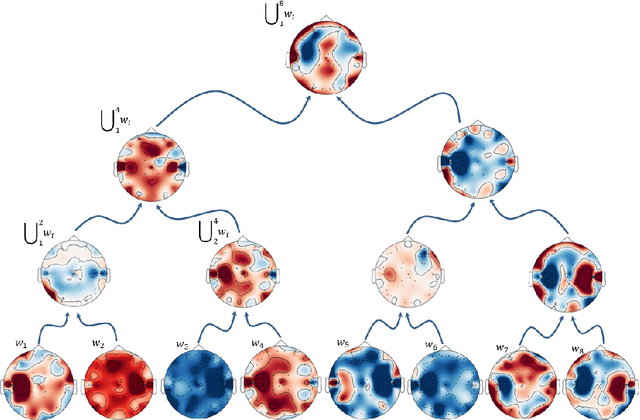

Abstract:We show that fMRI analysis using machine learning tools are sufficient to distinguish valence (i.e., positive or negative) of freely retrieved autobiographical memories in a cross-participant setting. Our methodology uses feature selection (ReliefF) in combination with boosting methods, both applied directly to data represented in voxel space. In previous work using the same data set, Nawa and Ando showed that whole-brain based classification could achieve above-chance classification accuracy only when both training and testing data came from the same individual. In a cross-participant setting, classification results were not statistically significant. Additionally, on average the classification accuracy obtained when using ReliefF is substantially higher than previous results - 81% for the within-participant classification, and 62% for the cross-participant classification. Furthermore, since features are defined in voxel space, it is possible to show brain maps indicating the regions of that are most relevant in determining the results of the classification. Interestingly, the voxels that were selected using the proposed computational pipeline seem to be consistent with current neurophysiological theories regarding the brain regions actively involved in autobiographical memory processes.

Features and Machine Learning for Correlating and Classifying between Brain Areas and Dyslexia

Jan 17, 2019

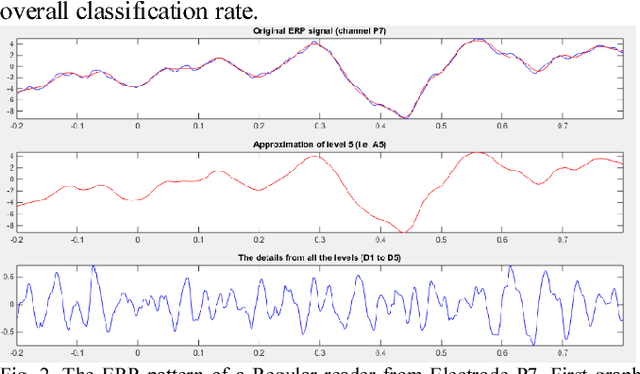

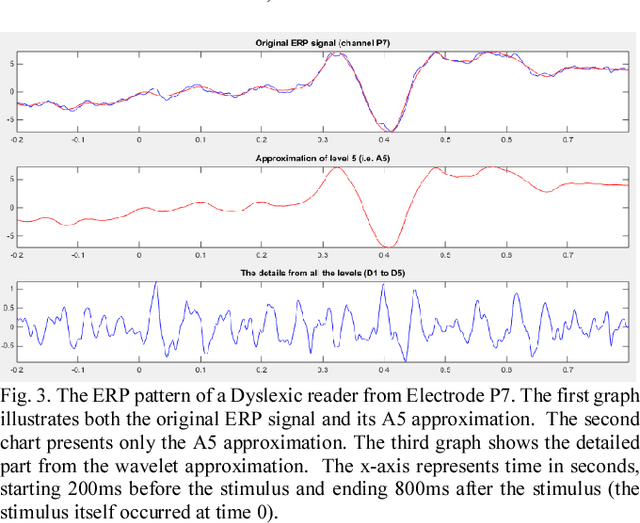

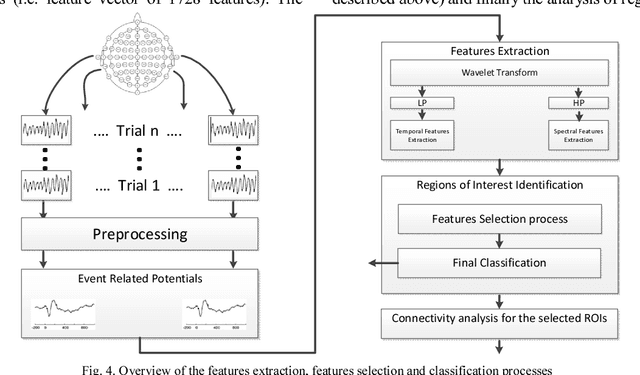

Abstract:We develop a method that is based on processing gathered Event Related Potentials (ERP) signals and the use of machine learning technique for multivariate analysis (i.e. classification) that we apply in order to analyze the differences between Dyslexic and Skilled readers. No human intervention is needed in the analysis process. This is the state of the art results for automatic identification of Dyslexic readers using a Lexical Decision Task. We use mathematical and machine learning based techniques to automatically discover novel complex features that (i) allow for reliable distinction between Dyslexic and Normal Control Skilled readers and (ii) to validate the assumption that the most of the differences between Dyslexic and Skilled readers located in the left hemisphere. Interestingly, these tools also pointed to the fact that High Pass signals (typically considered as "noise" during ERP/EEG analyses) in fact contains significant relevant information. Finally, the proposed scheme can be used for analysis of any ERP based studies.

Real-Time EEG Classification via Coresets for BCI Applications

Jan 02, 2019

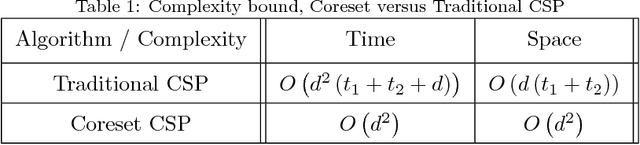

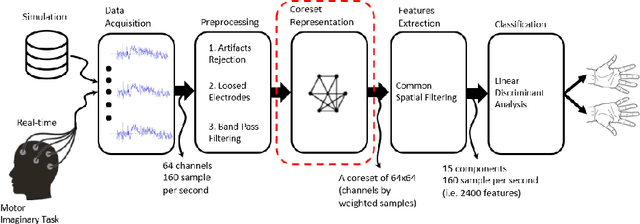

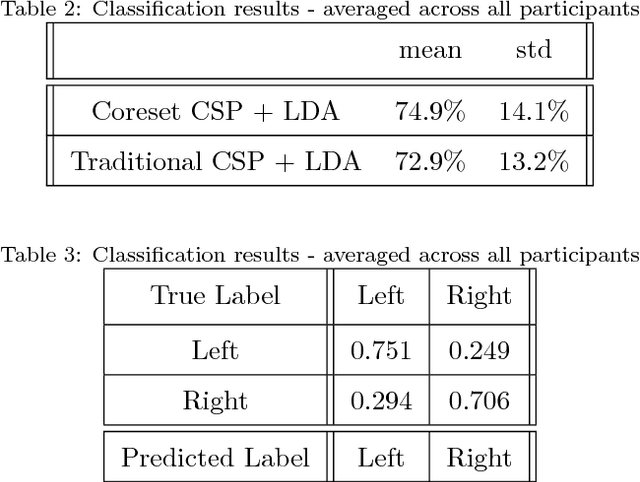

Abstract:A brain-computer interface (BCI) based on the motor imagery (MI) paradigm translates one's motor intention into a control signal by classifying the Electroencephalogram (EEG) signal of different tasks. However, most existing systems either (i) use a high-quality algorithm to train the data off-line and run only classification in real-time, since the off-line algorithm is too slow, or (ii) use low-quality heuristics that are sufficiently fast for real-time training but introduces relatively large classification error. In this work, we propose a novel processing pipeline that allows real-time and parallel learning of EEG signals using high-quality but possibly inefficient algorithms. This is done by forging a link between BCI and core-sets, a technique that originated in computational geometry for handling streaming data via data summarization. We suggest an algorithm that maintains the representation such coreset tailored to handle the EEG signal which enables: (i) real time and continuous computation of the Common Spatial Pattern (CSP) feature extraction method on a coreset representation of the signal (instead on the signal itself) , (ii) improvement of the CSP algorithm efficiency with provable guarantees by applying CSP algorithm on the coreset, and (iii) real time addition of the data trials (EEG data windows) to the coreset. For simplicity, we focus on the CSP algorithm, which is a classic algorithm. Nevertheless, we expect that our coreset will be extended to other algorithms in future papers. In the experimental results we show that our system can indeed learn EEG signals in real-time for example a 64 channels setup with hundreds of time samples per second. Full open source is provided to reproduce the experiment and in the hope that it will be used and extended to more coresets and BCI applications in the future.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge