S. Kempf

Institute of Micro- and Nanoelectronic Systems - Karlsruhe Institute of Technology - Germany, Institute for Data Processing and Electronics - Karlsruhe Institute of Technology - Germany

Full-Scale Readout Electronics for the ECHo-100k Experiment

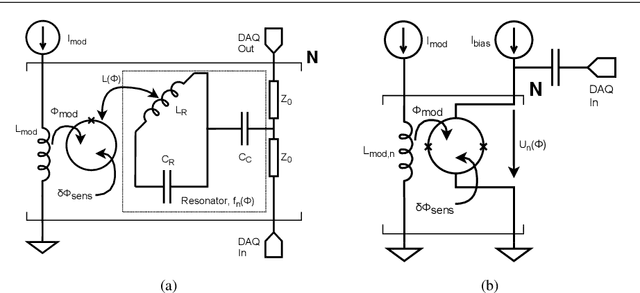

Apr 03, 2024Abstract:Recent advances in the development of cryogenic particle detectors such as magnetic microcalorimeters (MMCs) allow the fabrication of sensor arrays with an increasing number of pixels. Since these detectors must be operated at the lowest temperatures, the readout of large detector arrays is still quite challenging. This is especially true for the ECHo experiment, which presently aims to simultaneously run 6,000 two-pixel detectors to investigate the electron neutrino mass. For this reason, we developed a readout system based on a microwave SQUID multiplexer ($\mu$MUX) that is operated by a custom software-defined radio (SDR) at room-temperature. The SDR readout electronics consist of three distinct hardware units: a data processing board with a Xilinx ZynqUS+ MPSoC; a converter board that features DACs, ADCs, and a coherent clock distribution network; and a radio frequency front-end board to translate the signals between the baseband and the microwave domains. Here, we describe the characteristics of the full-scale SDR system. First, the generated frequency comb for driving the $\mu$MUX was evaluated. Subsequently, by operating the SDR in direct loopback, the crosstalk of the individual channels after frequency demultiplexing was investigated. Finally, the system was used with a 16-channel $\mu$MUX to evaluate the linearity of the SDR, and the noise contributed to the overall readout setup.

Online Demodulation and Trigger for Flux-ramp Modulated SQUID Signals

Oct 22, 2021

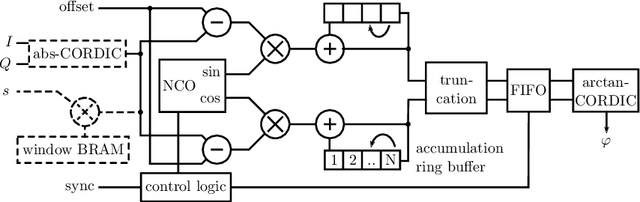

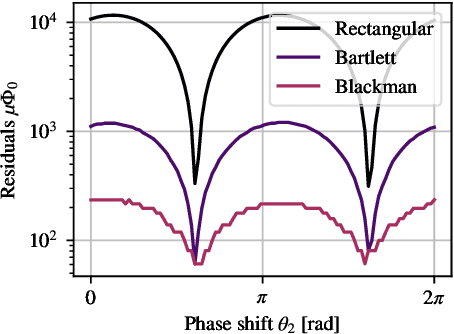

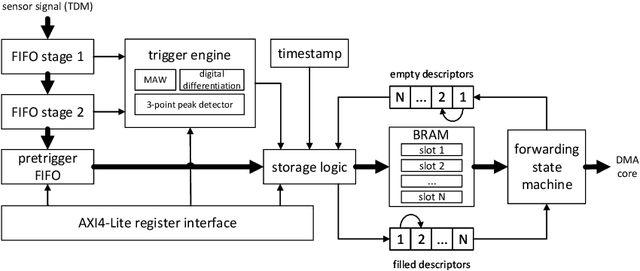

Abstract:Due to the periodic characteristics of SQUIDs, a suitable linearization technique is required for SQUID-based readout. Flux-ramp modulation is a common linearization technique and is typically applied for the readout of a microwave-SQUID-multiplexer as well as since recently also for dc-SQUIDs. Flux-ramp modulation requires another stage in the signal processing chain to demodulate the SQUID output signal before further processing. For cryogenic microcalorimenters, these events are given by fast exponentially rising and slowly exponentially decaying pulses which shall be detected by a trigger engine and recorded by a storage logic. Since the data rate can be decreased significantly by demodulation and event detection, it is desirable to do both steps on the deployed fast FPGA logic during measurement before passing the data to a general-purpose processor. In this contribution, we show the implementation of efficient multi-channel flux-ramp demodulation computed at run-time on a SoC-FPGA. Furthermore, a concept and implementation for an online trigger and buffer mechanism with its theoretical trigger loss rates depending on buffer size is presented. Both FPGA modules can be operated with up to 500 MHz clock frequency and can efficiently process 32 channels. Correct functionality and data reduction capability of the modules are demonstrated in measurements utilizing magnetic microcalorimeter irradiated with an Iron-55 source for event generation and read out by a microwave SQUID multiplexer.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge