Luke Theogarajan

The Gaussian-Multinoulli Restricted Boltzmann Machine: A Potts Model Extension of the GRBM

May 16, 2025Abstract:Many real-world tasks, from associative memory to symbolic reasoning, demand discrete, structured representations that standard continuous latent models struggle to express naturally. We introduce the Gaussian-Multinoulli Restricted Boltzmann Machine (GM-RBM), a generative energy-based model that extends the Gaussian-Bernoulli RBM (GB-RBM) by replacing binary hidden units with $q$-state Potts variables. This modification enables a combinatorially richer latent space and supports learning over multivalued, interpretable latent concepts. We formally derive GM-RBM's energy function, learning dynamics, and conditional distributions, showing that it preserves tractable inference and training through contrastive divergence. Empirically, we demonstrate that GM-RBMs model complex multimodal distributions more effectively than binary RBMs, outperforming them on tasks involving analogical recall and structured memory. Our results highlight GM-RBMs as a scalable framework for discrete latent inference with enhanced expressiveness and interoperability.

A CMOS Probabilistic Computing Chip With In-situ hardware Aware Learning

Apr 18, 2025Abstract:This paper demonstrates a probabilistic bit physics inspired solver with 440 spins configured in a Chimera graph, occupying an area of 0.44 mm^2. Area efficiency is maximized through a current-mode implementation of the neuron update circuit, standard cell design for analog blocks pitch-matched to digital blocks, and a shared power supply for both digital and analog components. Process variation related mismatches introduced by this approach are effectively mitigated using a hardware aware contrastive divergence algorithm during training. We validate the chip's ability to perform probabilistic computing tasks such as modeling logic gates and full adders, as well as optimization tasks such as MaxCut, demonstrating its potential for AI and machine learning applications.

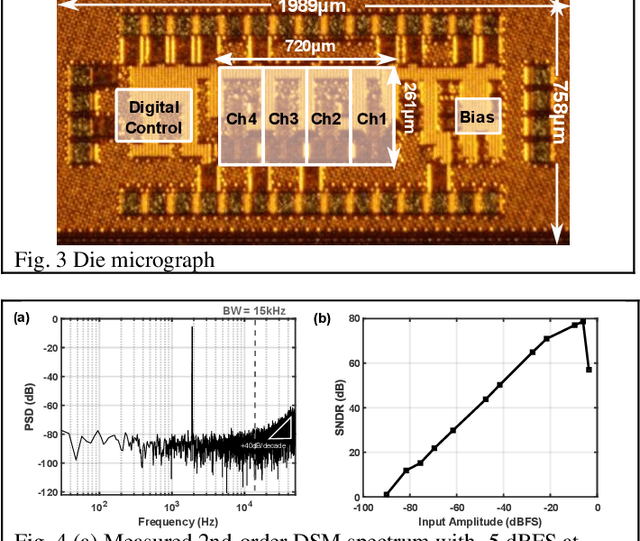

A 125$μ$W 8kS/s Sub-pA Area-Efficient Current Sensing 45nm CMOS ADC for Biosensing

Jul 13, 2021

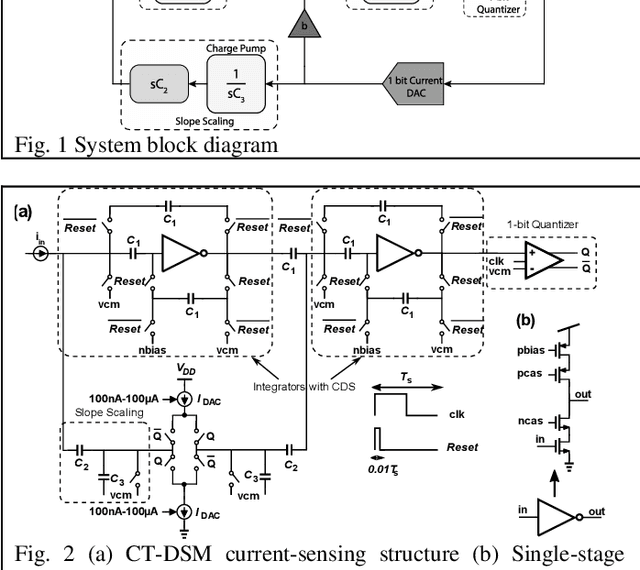

Abstract:This paper presents a 125$\mu$W, area efficient (0.042mm2) 81dB DR, 8kS/s current sensing ADC in 45nm CMOS capable of sensing sub-pA currents. Our approach combines the transimpedance amplifier (TIA) and ADC into a unified structure by folding a low-noise capacitive TIA into the first stage integrator of a 2nd order Delta-Sigma modulator. The dominant DAC feedback noise is mitigated by utilizing current scaling via slope modification by an integrator and differentiator pair.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge