Lucas Moura Santana

A technique to enable frequency dependent power savings in a level crossing analog-to-digital converter

Aug 17, 2021

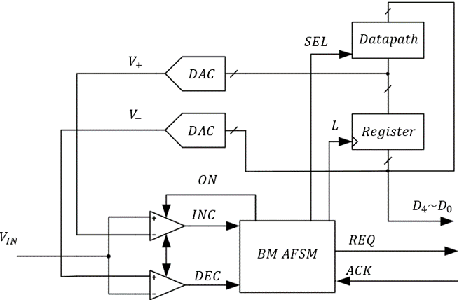

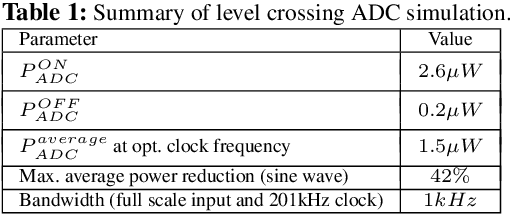

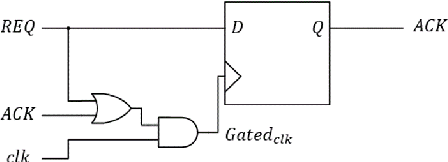

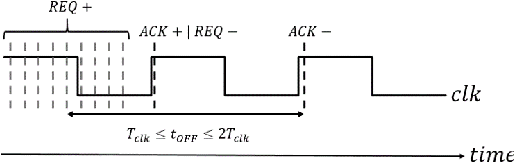

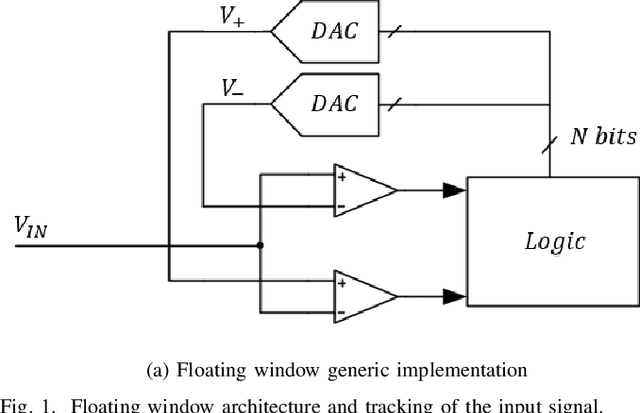

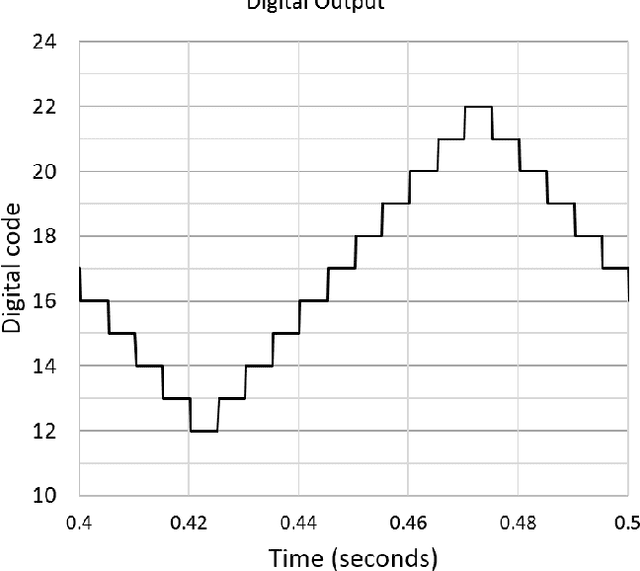

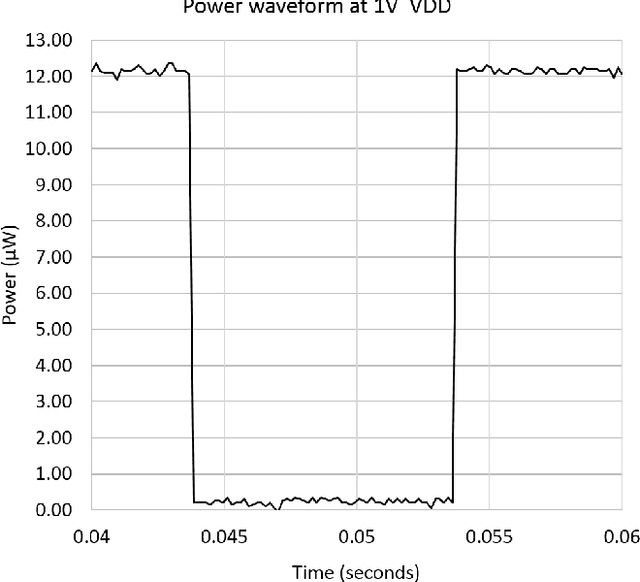

Abstract:The level crossing analog-to-digital converters are meant for the effective conversion of sparse signals by construction. In these converters, the bandwidth-power trade-off requires a re-design of the comparators which takes a lot of time and effort to reach the application optimum point. Inspired by synchronous converters that have a dynamic power component that can be traded with bandwidth with the change of a clock frequency, a technique to allow such trade-off in the level crossing converter was developed. The resulting level crossing ADC has an input signal dependent dynamic power which can reach up to 42\% OFF time during the conversion of sine waves, achieving 45.5% power reduction in the simulated design with TSMC 180nm PDK.

A 1V 5-bits Low Power Level Crossing ADC with OFF state in idle time for bio-medical applications in 0.18um CMOS

Aug 17, 2021

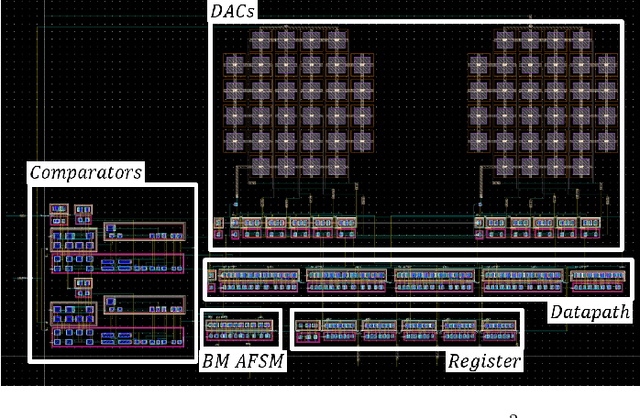

Abstract:The ubiquitous use of sensing and signal processing is increasing exponentially with the advance of the Internet of Everything (IoE). In this context, the design of every time more power efficient sensor nodes is a must. Within these nodes, one of the most power-hungry components are the analog-to-digital converters (ADC). These components are used everywhere to translate real-world analog signals into computer intelligible digital signals. One of the promising architecture for the sensing of physiological signals is the level crossing ADC due to the sparse characteristics of those signals. One of the challenges to improve the power efficiency of this type of ADC lies in the use of continuous comparators to keep track of the input signal within the voltage references. The aim of this work is to investigate the impact of using continuous comparator which can be turned off without incurring error to the conversion of the level crossing ADC. New boundaries will be set for the correct behavior of the level crossing ADC together with the conditions for power saving with the proposed architecture. A 1V 5-bits level crossing ADC was implemented using the TSMC 0.18um process and fabricated for laboratory measurements. The ADC consumes 12.2uW during tracking state and with the proposed technique, the reduction of the average power can go from 4.2% to 45.5% depending on the activity and the type of the input signal.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge