Giovanni Del Galdo

Joint Delay-Doppler Estimation using OFDMA Payloads for Integrated Sensing and Communications

Mar 06, 2025

Abstract:The use of future communication systems for sensing offers the potential for a number of new applications. In this paper, we show that leveraging user data payloads in multi-node Orthogonal Frequency Division Multiple Access (OFDMA) networks for estimating target delay and Doppler-shift parameters can yield a significant advantage in SNR and addressable bandwidth. However, gaps in the frequency-time resources, reference signal boosting and amplitude modulation schemes introduce challenges for estimation at the sensing receiver. In this work, we propose a joint delay and Doppler-shift model-based estimator designed to address these challenges. Furthermore, we demonstrate that incorporating knowledge of the device model into the estimation procedure helps mitigate the effects of the non-ideal radar ambiguity function caused by amplitude-modulated user payloads and sparse reference signals. Simulation results demonstrate that the estimator achieves the theoretical lower bound on estimation variance.

Misspecification of Multiple Scattering in Scalar Wave Fields and its Impact in Ultrasound Tomography

May 02, 2024

Abstract:In this work, we investigate the localization of targets in the presence of multiple scattering. We focus on the often omitted scenario in which measurement data is affected by multiple scattering, and a simpler model is employed in the estimation. We study the impact of such model mismatch by means of the Misspecified Cram\'er-Rao Bound (MCRB). In numerical simulations inspired by tomographic inspection in ultrasound nondestructive testing, the MCRB is shown to correctly describe the estimation variance of localization parameters under misspecification of the wave propagation model. We provide extensive discussion on the utility of the MCRB in the practical task of verifying whether a chosen misspecified model is suitable for localization based on the properties of the maximum likelihood estimator and the nuanced distinction between bias and parameter space differences. Finally, we highlight that careful interpretation is needed whenever employing the classical CRB in the presence of mismatch through numerical examples based on the Born approximation and other simplified propagation models stemming from it.

Accelerating Innovation in 6G Research: Real-Time Capable SDR System Architecture for Rapid Prototyping

Feb 22, 2024

Abstract:The next global mobile communication standard 6G strives to push the technological limits of radio frequency (RF) communication even further than its predecessors: Data rates beyond 100 Gbit/s, RF bandwidths above 1 GHz, and sub-millisecond latency necessitate very high performance development tools to enable the extent of innovation required for 6G's likely features. We propose a new SDR firmware and software architecture designed explicitly to meet these challenging requirements. It relies on Ethernet and commercial off-the-shelf network and server components to maximize flexibility and to reduce costs. We analyze state-of-the-art solutions (USRP X440 and other RFSoC-based systems), derive architectural design goals, explain resulting design decision in detail, and exemplify our architecture's implementation on the XCZU48DR RFSoC. Finally, we prove its performance via measurements and outline how the architecture surpasses the state-of-the-art with respect to sustained RF recording while maintaining high Ethernet bandwidth efficiency. Building a micro-Doppler radar example, we demonstrate its real-time and rapid application development capabilities.

Low-Latency Analog-to-Analog Signal Processing using PC Hardware and USRPs

Oct 12, 2022

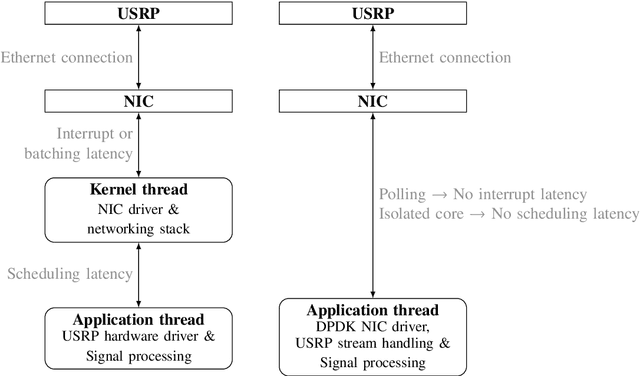

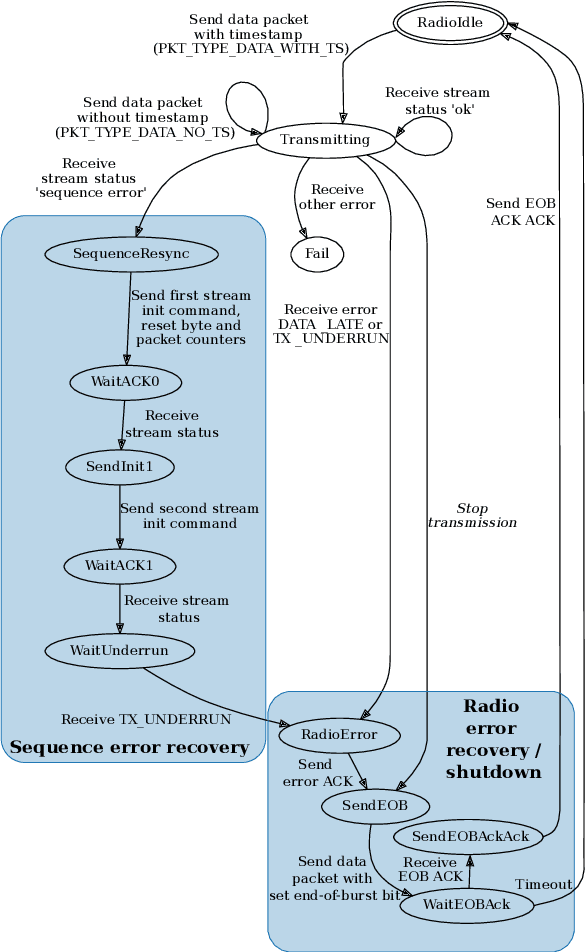

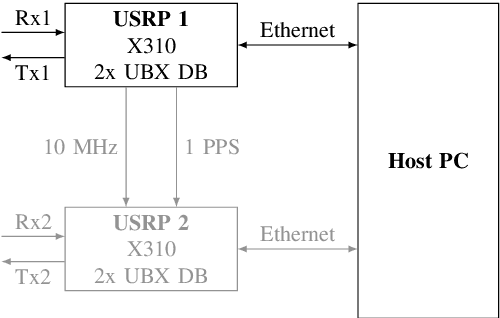

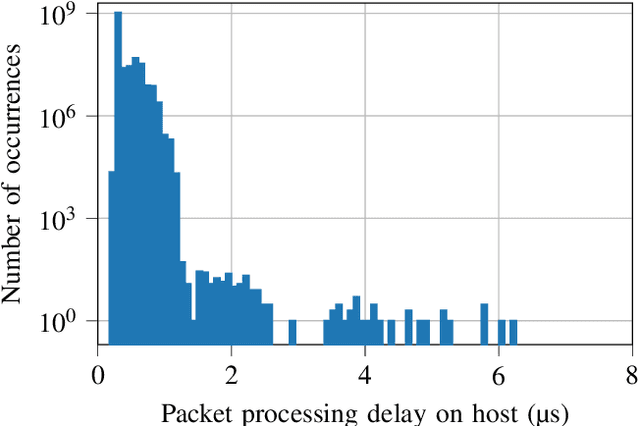

Abstract:In this paper, we implement a low-latency rapid-prototyping platform for signal processing based on software-defined radios (SDRs) and off-the-shelf PC hardware. This platform allows to evaluate a wide variety of algorithms in real-time environments, supporting new developments in the fields of classical, AI-based, and hybrid signal processing. To accomplish this, the streaming protocol of the used USRP X310 devices is implemented using the Data Plane Development Kit (DPDK), which allows to handle network communication in userspace only. This bypasses the kernel and thus avoids the latencies caused by interrupt handling, scheduling, and context switches. It allows signal processing to be performed on isolated processor cores that are protected from interrupts to a great extent. To validate our approach, linear time-invariant channel emulation has been implemented. For this, an analog-to-analog latency of 31 microseconds was achieved, demonstrating that our PC-based approach enables the implementation of rapid-prototyping systems with low latency.

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge