Akshay Kumar Maan

Memristive Threshold Logic Circuit Design of Fast Moving Object Detection

Oct 06, 2014

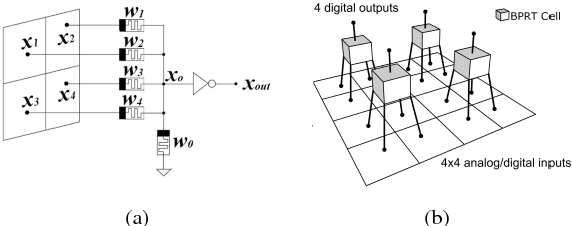

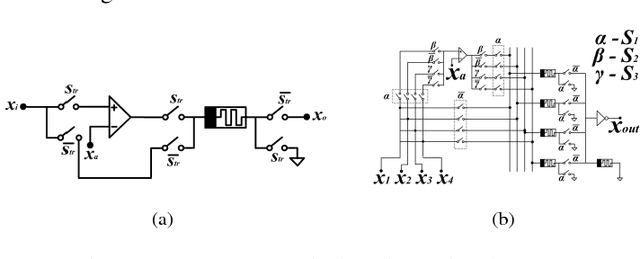

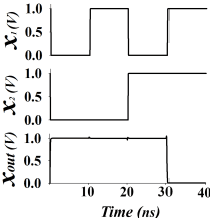

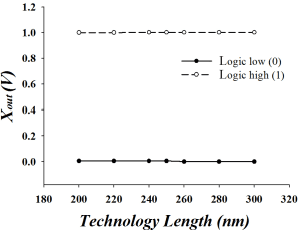

Abstract:Real-time detection of moving objects involves memorisation of features in the template image and their comparison with those in the test image. At high sampling rates, such techniques face the problems of high algorithmic complexity and component delays. We present a new resistive switching based threshold logic cell which encodes the pixels of a template image. The cell comprises a voltage divider circuit that programs the resistances of the memristors arranged in a single node threshold logic network and the output is encoded as a binary value using a CMOS inverter gate. When a test image is applied to the template-programmed cell, a mismatch in the respective pixels is seen as a change in the output voltage of the cell. The proposed cell when compared with CMOS equivalent implementation shows improved performance in area, leakage power, power dissipation and delay.

A Neuron Based Switch: Application to Low Power Mixed Signal Circuits

Jan 28, 2012

Abstract:Human brain is functionally and physically complex. This 'complexity' can be seen as a result of biological design process involving extensive use of concepts such as modularity and hierarchy. Over the past decade, deeper insights into the functioning of cortical neurons have led to the development of models that can be implemented in hardware. The implementation of biologically inspired spiking neuron networks in silicon can provide solutions to difficult cognitive tasks. The work reported in this paper is an application of a VLSI cortical neuron model for low power design. The VLSI implementation shown in this paper is based on the spike and burst firing pattern of cortex and follows the Izhikevich neuron model. This model is applied to a DC differential amplifier as practical application of power reduction

Add to Chrome

Add to Chrome Add to Firefox

Add to Firefox Add to Edge

Add to Edge